Document Outline

- Features

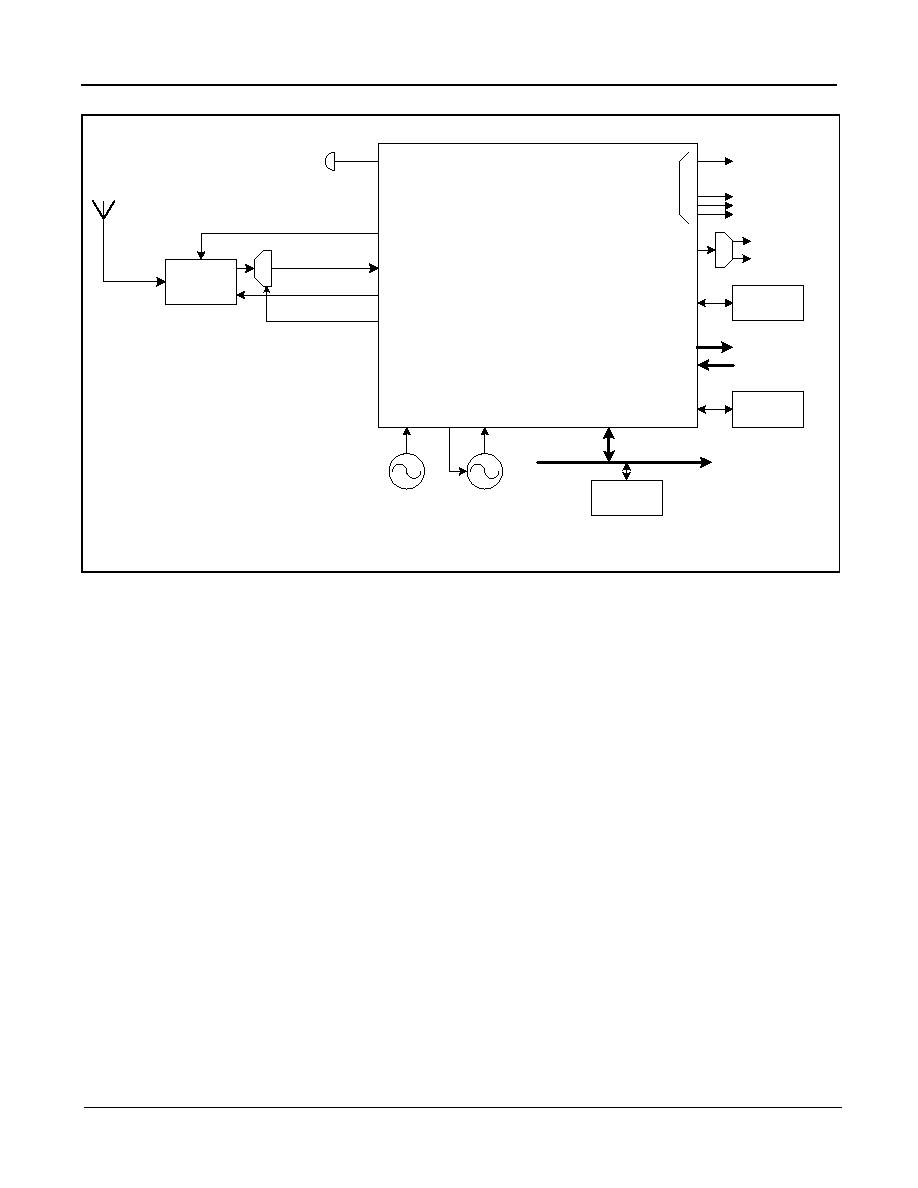

- Figure 1 - Block Diagram of ZL10310 and ZL10311

- Applications

- Description

- 1.0 Device Overview

- 2.0 Device Interfaces

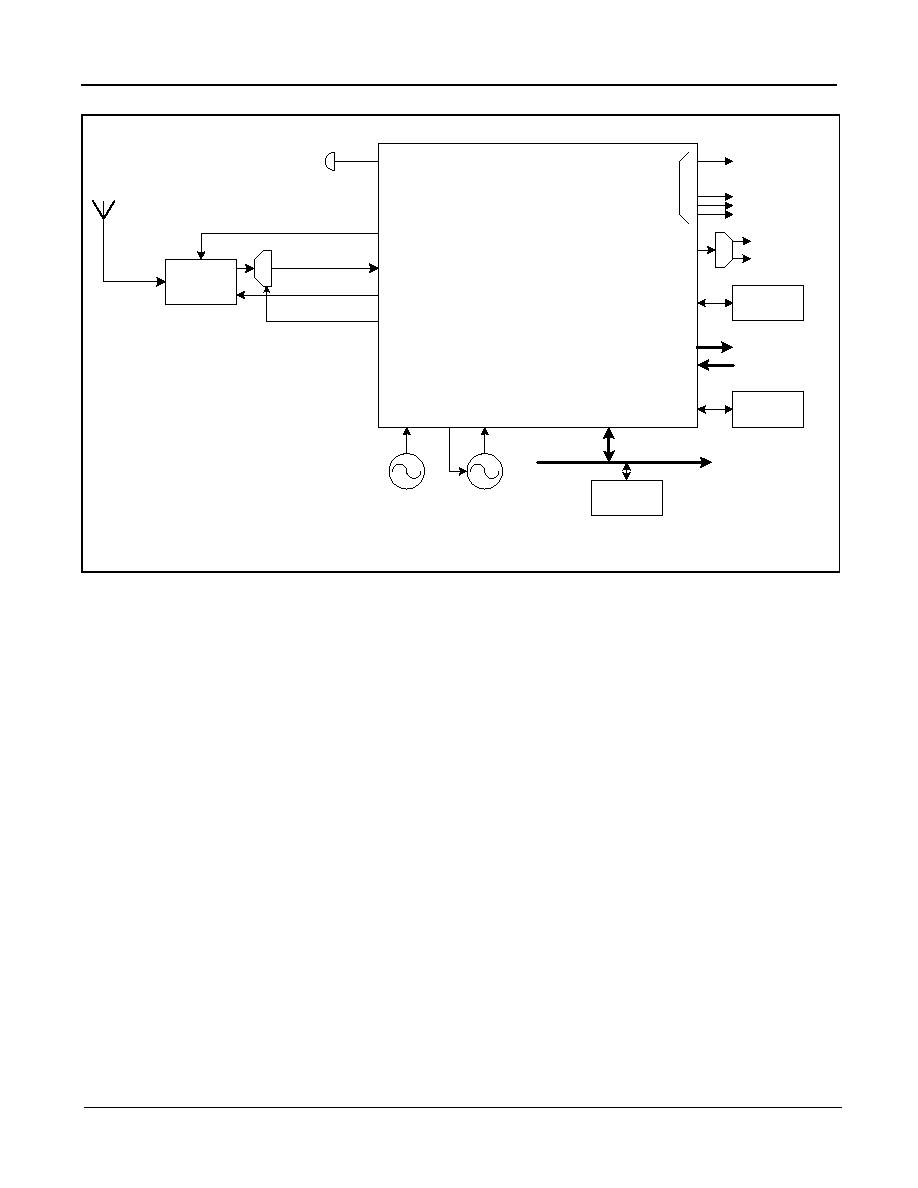

- Figure 2 - Block diagram of a typical ZL10310-based Free to Air TV Adaptor

- 3.0 Typical Digital Television (DTV) Receiver

- 4.0 Functional Blocks Overview

- 4.1 Boot ROM

- 4.2 Clock Generation Block

- 4.3 Coded Orthogonal Frequency Division Multiplex (COFDM) Demodulator

- 4.4 MPEG Audio Decoder

- 4.5 MPEG-2 Video Decoder

- 4.6 PowerPC 405TM Processor

- 4.7 Transport Engine

- 4.8 Video Display System

- 5.0 Physical Specification

- Figure 3 - Package View and Ball Positions

- 6.0 ZL10310/ZL10311 388-pin Package Pin Descriptions

- 6.1 Pin Types

- 6.2 Front End Interfaces

- 6.3 Video DAC Outputs

- 6.4 SDRAM Interfaces

- 6.5 Bit Stream Interfaces

- 6.6 Auxiliary External Bus

- 6.7 Peripheral Port

- 6.8 Modem/Codec Interface

- 6.9 Smart Card Interface

- 6.10 General Purpose Input Output Interfaces

- 6.11 Simplified General Purpose Input Output Interface

- 6.12 Inter Integrated Circuit (I2C) Interface

- 6.13 Inter IC Sound (I2S) Audio Interface

- 6.14 Clock and Reset Interface

- 6.15 Power Supply Pins

- 6.16 Reserved Connections

- 7.0 Characteristics

- 7.1 AC and DC Electrical Characteristics

1

Features

∑ DTV-SoC for Digital Terrestrial Television (DTT)

∑ On-chip DVB-T COFDM demodulator with FEC.

∑ 6 Video DACs on-chip, for Composite or

Component (RGB or Y U/V) Analog Video

∑ Twin PAL/NTSC DENCs

∑ Low Power (<1.4W Typical)

∑ Low Component Count

∑ Unified SDRAM controller

∑ I

2

S Digital Audio Input

∑ I

2

S and S/PDIF Digital Audio outputs

∑ MPEG-2 Audio & Video decoders

∑ PowerPC 405

TM

CPU Core with 16k/16k cache,

Memory manager and Virtual memory system

∑ Complete Linux-based Software Development Kit

(SDK)

∑ IDE interface

∑ Inputs for external MPEG-2 Transport Streams,

allowing support for external demodulators (e.g.

Cable TV, Satellite TV)

∑ Conditional Access (CA) DVB-descrambler

∑ Smart Card Interface

∑ Infrared & UART interface

∑ DVB-compatible Common Interface (CI) control

and bitstream interfaces

∑ Multi-stream multiplexing to support internal and

external demodulators

∑ External Modem support interface

∑ Supports Macrovision

TM

Copy Protection -

(ZL10311 only; available to Macrovision license

holders only)

∑ Dolby

Digital* Decoding - (ZL10311 only;

available to Dolby

Digital* license holders only -

*awaiting certification)

Issue 1.0

November 2002

Ordering Information

ZL10310/GAC 388 ball EPBGA

ZL10311/GAC 388 ball EPBGA

0

0

C to +70

0

C

ZL10310/ZL10311

Digital Television DVB-T-On-a-Chip

Processor

Data Sheet

Figure 1 - Block Diagram of ZL10310 and ZL10311

AUX Bus

SDRAM 1

BUS

Bitstream

O/P

/Second

Smart Card

Bitstream

I/P

Bitstream

Multiplexing &

Control

Peripherals

Flash

IDE

CI Control

System

DeMultiplex

De-

scrambler

Audio

Decoder

Cached

PowerPC 405

Sub System

COFDM

DeModulator

& FEC

AGC B

SDRAM

Controller

Video Scaler

/ Blender

Stereo Audio

DAC

I S

2

Comp

Video

Y+U/V

RGB

Analog

Video

De-mod

/JTAG

ADC IN

/De-mod

JTAG

R

Smart Card

CODEC/modem

I C

UART/IRDA

BIT I/O

2

SDRAM

Controller

SDRAM 0

BUS

(optional)

Video

Decoder

8k Boot

ROM

Power Management

ADCIN

EXTIN

S/PDIF

ZL10310 / ZL10311 DTV-SOC

Video

DENCs

/DACs

ZL10310/ZL10311

Data Sheet

2

Zarlink Semiconductor Inc.

Applications

∑ Low power, small footprint TV adaptors

∑ Integrated Digital Televisions (iDTV)

∑ Digital terrestrial set-top boxes

∑ DTT / DVD Combo

∑ DVB-T radio receivers

∑ Terrestrial / Satellite Combo

∑ Terrestrial / Cable Combo

∑ Terrestrial / IP (Internet Protocol) Combo

Description

Zarlink Semiconductor has responded to market demand by integrating its key DVB-T compliant COFDM

demodulation technology with Set Top Box functionality (MPEG-2 A/V decoder and system interfaces) together with

a high performance CPU to offer a "DVB-T On-a-Chip" solution.

The ZL10310 DVB-T On-a-Chip, can address a wide range of DVB-T consumer electronic products. At the entry

level it can be used to build ultra-compact Free-To-View Digital TV adaptors (such as for FreeView in the UK), yet

consumes less than 4W of power in full operational mode.

This level of compactness also considerably eases the integration of DVB-T receiver technology inside integrated

Digital TV sets (iDTV's) where space considerations and thermal management are key design issues.

The ZL10310 is based upon an industry standard PowerPC 405

TM

RISC processor, which has Virtual and Memory

Management sub-systems. This permits the device to be effectively deployed in compelling applications such as

interactive Digital TV which are able to exploit the superior processing performance offered by the PowerPC

processor core.

The PowerPC

provides an ideal platform for running robust open standard operating systems such as Linux which

can benefit system developers in a number of key areas:

∑ Unified software development environment, from entry level basic channel zapper systems through to fully

interactive high performance Digital Set Top Boxes.

∑ Re-use of software code from multiple projects

∑ Exploit software code developed in the Linux community.

∑ Low cost-per-seat software development environment.

∑ Familiar software development environment.

∑ Royalty free.

Also available is the ZL10311 DVB-T On-a-Chip, which additionally offers Dolby

Digital

1

multi-channel audio

decoding, and Macrovision

TM

Copy Protection for applications requiring Dolby

Audio and Pay TV services.

1. The ZL10311 device is awaiting Dolby Certification

Data Sheet

ZL10310/ZL10311

3

Zarlink Semiconductor Inc.

Table of Contents

1.0 Device Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.0 Device Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.0 Typical Digital Television (DTV) Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

4.0 Functional Blocks Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4.1 Boot ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4.2 Clock Generation Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4.3 Coded Orthogonal Frequency Division Multiplex (COFDM) Demodulator . . . . . . . . . . . . . . . . . . . . . . . . . 7

4.4 MPEG Audio Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4.5 MPEG-2 Video Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4.6 PowerPC 405TM Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4.7 Transport Engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4.8 Video Display System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

5.0 Physical Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

6.0 ZL10310/ZL10311 388-pin Package Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

6.1 Pin Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

6.2 Front End Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

6.3 Video DAC Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6.4 SDRAM Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.5 Bit Stream Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

6.6 Auxiliary External Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

6.7 Peripheral Port. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

6.8 Modem/Codec Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

6.9 Smart Card Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.10 General Purpose Input Output Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.11 Simplified General Purpose Input Output Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

6.12 Inter Integrated Circuit (I2C) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

6.13 Inter IC Sound (I2S) Audio Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

6.14 Clock and Reset Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

6.15 Power Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.16 Reserved Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

7.0 Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

7.1 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

IBM

Æ

, the IBM Logo, PowerPC

Æ

and PowerPC405

TM

are trademarks of International Business Machines

Corporation.

Dolby

is a trademark of Dolby Laboratories. Supply of this implementation of Dolby Technology does not convey a

license or imply a right under any patent, or any other Industrial or Intellectual Property Right of Dolby Laboratories,

to use this implementation in any finished end-user or ready-to-use final product. It is hereby notified that a license

for such use is required from Dolby Laboratories

1

.

This device is protected by US patent numbers 4631603, 4577216 and 4819098 and other intellectual property

rights. Use of the Macrovision anticopy process in the device is licensed by Macrovision for non-commercial, home

and limited exhibition use only. Reverse engineering or disassembly is prohibited. A valid Macrovision license must

be in effect between the purchaser of the ZL10311 IC and Macrovision Corporation. Additional per-chip royalties

may be required and are payable by the purchaser to Macrovision.

1. The ZL10311 device is awaiting Dolby Certification

ZL10310/ZL10311

Data Sheet

4

Zarlink Semiconductor Inc.

1.0 Device Overview

Zarlink Semiconductor has designed the ZL10310 and ZL10311 System On a Chip (SoC) devices specifically for

DVB-T applications. Integrating a high performance PowerPC 405

TM

processor with robust industry proven

MPEG-2 audio and video decoding, OSD and a COFDM demodulator, the ZL10310 and ZL10311 deliver the

performance and functionality required for advanced Digital TV entertainment products. It enables the rapid design

and manufacture of cost-effective iDTV and Digital Audio Visual Home Entertainment Centers.

The enhanced ZL10311 also supports DVD playback with up to six Dolby

Digital

1

audio channels. In addition, by

integrating the COFDM demodulator, the ZL10310 and ZL10311 enable the implementation of very small footprint

TV Adaptor modules.

2.0 Device Interfaces

The following peripheral interfaces are available to the user. Apart from possible level translation and connector

buffering, no external devices are required to support any of the interfaces.

∑ 10-bit input that may be configured for an ADC input to the internal COFDM demodulator

∑ Additional input bus for additional MPEG-2 Transport Sources

∑ AGC (PWM) outputs for a terrestrial tuner

∑ Serial control port for a digital tuners

∑ Common interface control and bitstream interfaces for an external descrambler

∑ Normal PC (PCMCIA) memory module interface for local software updates

∑ Unified 64 Mbit SDRAM interface for all decoders and PowerPC 405

TM

∑ Additional SDRAM interface for high end systems requiring increased memory bandwidth

∑ Static memory interface for Flash and external peripherals

∑ IDE/ATAPI interface for hard disk and DVD drives

∑ External DMA channel and interrupts

∑ Six analog video outputs give full flexibility on RGB, S-VHS, and composite signals (with and without OSD)

∑ I

2

S input port from external Digital Stereo source

∑ Three I

2

S ports to external audio DACs for main, surround, and centre channels

∑ Dolby

surround sound control signals

∑ Sony/Philips Digital InterFace (S/PDIF)

If not required in a particular system, any of the peripheral interfaces can be replaced by individual I/O bits from

internal general purpose registers. These can then be used for additional purpose, such as interfacing to switches

and displays.

∑ Full RS232 interface to an external modem or a 4 wire interface to a Codec

∑ IRDA interface or an additional asynchronous serial interface

∑ Synchronous serial interface for EEPROM, etc.

∑ Two Smart card Interfaces (one instead of a Common Interface)

∑ General purpose I

2

C interface

∑ General purpose timer for Infrared (IR) decoding

∑ General purpose individual bit I/Os

1. The ZL10311 device is awaiting Dolby Certification

Data Sheet

ZL10310/ZL10311

5

Zarlink Semiconductor Inc.

Figure 2 - Block diagram of a typical ZL10310-based Free to Air TV Adaptor

3.0 Typical Digital Television (DTV) Receiver

Figure 2 shows a typical Free to Air TV receiver block diagram employing a ZL10310 DTV-SoC device. In its

minimal configuration, the ZL10310 DTV-SoC device only requires a single 64 Mbit SDRAM, an audio DAC, and a

Flash ROM, which are in addition to a DVB-T tuner front end and a 10-bit analog to digital converter.

The Terrestrial Tuner section performs an independent down conversion of the received DVB-T signal from the

Antenna, to an IF frequency in the range of 30MHz to 57MHz, dependent on television system (typically 36.17MHz

Center Frequency, with

±4MHz span). The analogue IF is then converted to the digital domain, with a 10-bit ADC,

clocked at 20.48MHz and the resulting Digital output is centered on 15.69MHz. This Digital signal is applied to the

ZL10310 via the ADC_IN[9:0] input pins, in the form of a 10-bit parallel signal.

The ZL10310 converts the digitized IF from a Terrestrial TV Tuner into an MPEG-2 Transport Stream, which can be

optionally de-scrambled (if CA scrambling is used by the broadcaster), and de-multiplexed into separate Packetised

Elementary Streams (PES), which are routed to the MPEG Audio and Video decoders, and SI data to the PowerPC

405

TM

subsystem.

Decoded Video can then be mixed and optionally scaled with On-Screen Display (OSD) Graphics generated by the

DTV application software. The resultant combination of video and graphics are then routed to the PAL/NTSC Digital

ENCoders (DENCs) for display on the TV via the on-chip 10-bit video DACs.

Decoded Audio is output directly from the audio decoder sub-system to the I

2

S and S/PDIF (Sony/Philips Digital

InterFace) outputs.

ZL10310

DTV-SOC

Comp Video

Analog Video

RGB or Y U/V

Digital Audio

(I S)

D

A

C

Analog Audio

2

Aux Bus

Aux

Bus

8MB

FLASH

External

Peripherals

SDRAM

SDRAM1

Bus

Er

r

o

r

27MHz

VCXO

CLK

27IN

20.48MHz

Crystal

Oscillator

COFDM

Clock

Terrestrial

Tuner

ADCIN

AGC B

ADCCLK

A

D

C

20.48MHz

Bitstream o/ps

Bitstream i/ps

Common

Interface

Tuner Control

Serial

EEPROM

InfraRed Sensor